| Aeronautica | Comunicatii | Drept | Informatica | Nutritie | Sociologie |

| Tehnica mecanica |

Informatica

|

|

Qdidactic » stiinta & tehnica » informatica tehnician mecatronist - microprocesoare- evolutii si tipuri |

tehnician mecatronist - microprocesoare- evolutii si tipuri

Colegiul Tehnic "Dimitrie Leonida" Iasi

PROIECT

PENTRU OBTINEREA CERTIFICATULUI DE

COMPETENTE PROFESIONALE NIVEL 3

Calificarea: Tehnician mecatronist

MICROPROCESOARE- EVOLUTII SI

TIPURI

1. MEMORIU JUSTIFICATIV

Am ales sa dezbat aceasta tema deoarece computerele din ziua de azi nu sunt numai cele mai bune masinarii proiectate de cei mai buni ingineri si programatori. Ele sunt produsul unei evolutii care s-a bazat atat pe capricii considerente comerciale, cat si pe inovatii tehnologice care mi-au atras atentia. Istoria bogata si complexa a procesoarelor moderne se intinde pe mai bine de o jumatate de secol, inceputurile acesteia fiind indisolubil legate de calculatoarele care au deschis noi cai in era informaticii.

Procesorul a aparut ca urmare a necesitatii efectuarii in mod rapid de calcule complexe si a avut o ascensiune si perfectionare simultana cu dezvoltarea industriei mondiale de informatica si telecomunicatii.

Microprocesorul este o componenta electronica ce poate procesa doua tipuri de informatie: date si comenzi; el primeste si trimite aceste informatii, codate in limbaj binar, prin impulsuri electrice. In ciuda complexitatii sale, microprocesorul este alcatuit in principal dintr-un singur element de baza: tranzistorul (inventat in 1947).

Acesta a evoluat intr-o perioda relativ scurta plecandu-se de la un procesor ce putea executa simultan maxim doua aplicatii si ajungandu-se la cele din ziua de azi.

EVOLUTIA MICROPROCESOARELOR

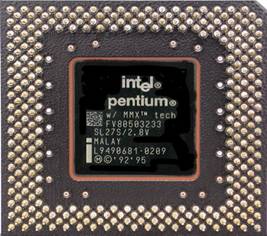

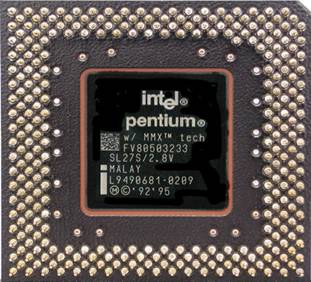

Intel Pentium (22 martie 1993)

Intel Pentium a fost primul procesor superscalar de la Intel (putea executa pana la doua instructiuni simultan). Multi s-au intrebat de ce Intel nu a denumit acest procesor 80586. Motivul a fost ca numele format numai din cifre nu putea fi protejat de copyright, asa ca Intel s-a vazut nevoit sa foloseasca si litere pentru a-si diferentia produsele de cele ale concurentei. Procesorul lucra cu o magistrala de date de 64 de biti (cu toate ca a fost un procesor pe 32 de biti) si a fost lansat initial la viteze de 60 si 66 de MHz. Au urmat insa foarte rapid versiuni de 75, 90, 100, 120, 133, 150, 166, 200, 233

MHZ. De fapt au existat trei versiuni de Pentium: prima versiune care nu cuprindea decat doua modele: Pentium la 60 si la 66MHz, a doua versiune care a adaugat instructiunile MMX si o ultima versiune care a micsorat distanta dintre tranzistoare permitand astfel viteze mai mari care au ajuns pana la 233MHz. Intel Pentium a fost primul microprocesor pentru PC-uri care putea sa calculeze mai mult de 100MIPS (milioane de instructiuni pe secunda). Tot pentru prima oara era posibila construirea unor sisteme care sa lucreze cu 2 procesoare in paralel (sisteme multiprocesor). Microprocesorul de la Intel venea cu 16Kb de cache incorporati in pastila de siliciu.

2.2 AMD K5 / Nexgen Nx586

AMD a reactionat destul de tarziu in a lansa un procesor comparabil ca viteza cu Intel Pentium. In 1995 a produs totusi primul sau procesor care era

conceput integral de catre ei, nemaifiind o simpla clona a procesoarelor Intel. Acest procesor s-a numit K5 si avea viteze de la 75 la 166MHz. Cu toate

acestea nu era un procesor mai rapid decat cele de la Intel, in plus avand o unitate de calcul in virgula mobila destul de slaba. Una din inovatiile aduse de K5 era faptul ca instructiunile x86 erau transformate intern in ROP (Risc OPerations). Aceste operatii RISC se puteau executa in nucleul RISC al procesorului care era mult mai rapid. In acelasi timp o companie de care putina lume auzise pana atunci, Nexgen, lansa primul sau procesor: Nx586. Complexitatea procesorului K5 a dus la frecvente destul de mici, ceea ce i-a facut pe cei de la AMD sa cumpere compania Nexgen care tocmai terminase design-ul noului lor procesor, NX686. Acest design a fost ulterior folosit de AMD in urmatoarea sa familie de procesoare pe care avea sa o lanseze in 1997.

Cyrix 6x86 (Octombrie 1995)

6x86 a fost replica lui Cyrix la

procesorul Pentium al lui Intel. Acest chip era produs initial de catre

IBM dat fiind ca Cyrix nu avea unitati de asamblare de procesoare,

insa ulterior, odata cu achizitionarea Cyrix de catre

National Semiconductor a fost produs chiar de catre acestia. Procesorul a avut un

succes destul de mare dat fiind ca era mai rapid decat un Intel Pentium la

aceeasi frecventa. De altfel pentru a-l putea compara cu

procesoarele de la Intel, cei de la Cyrix au inventat ceea ce s-a numit

ulterior P-Rating. De exemplu procesorul Cyrix 6x86 care functiona la 150

de MHz a fost denumit 6x86PR200, ceea ce insemna ca era comparabil ca

viteza cu un Pentium la 200. Unul din marile dezavantaje ale acestui

procesor a fost insa viteza foarte mica a calculelor in virgula

mobila. Cu toate acestea in aplicatiile de tip office s-a dovedit cel

putin la fel de rapid ca si un Pentium.

Intel Pentium Pro (1 noiembrie 1995)

Acest procesor a fost una dintre cele mai mari inovatii tehnice produse de Intel pana acum. Procesorul ingloba pentru prima oara in istorie pe langa

cache-ul Level1 de 8k pentru date si 8k pentru instructiuni, si un cache Level2 de 256Kb sau 512Kb. Folosea un sistem complex de predictie a ramurii de executie (branch prediction) si executie speculativa (speculative execution) - in momentul in care executia programului ajungea la o bifurcatie ramura corecta nu era stiuta pana in momentul in care se executa instructiunea conditionala; pentru ca procesorul sa nu astepte pana in acea clipa, se alegea una din cele doua ramuri si se incepea executia instructiunilor respective; daca se dovedea ca ramura aleasa a fost cea corecta aceasta insemna un castig important de viteza. Acest microprocesor transforma instructiunile x86 in microoperatii care erau mult mai mici si mai rapide. Acest lucru, cu toate ca

avea ca rezultat o viteza mult mai mare a instructiunilor de 32 de biti, a dus la performante mult mai slabe in sistemele de operare care mai contineau cod

pe 16 biti.

Intel Pentium MMX (Ianuarie 1997)

MMX s-a crezut initial ca inseamna MultiMedia eXtension, dar Intel a declarat ca inseamna Matrix Math eXtension. Acesta reprezinta un standard introdus de Intel care aduce cateva noi instructiuni care usurau in principal calculele matematice cu vectori.

AMD K6 (Aprilie 1997)

Ca urmare a cumpararii firmei Nexgen, AMD a reusit sa lanseze un nou procesor, K6 care avea viteze de la 166 la 266MHz. Bineinteles ca politica AMD a fost ca procesoarele sale sa se vanda la aproape jumatate din pretul la care se vindeau procesoarele Intel. K6 incorpora instructiuni MMX (a caror

licenta a cumparat-o de la Intel) devenind astfel un rival de temut pentru procesoarele Intel Pentium MMX.

Procesorul Cyrix 5x86

Familia de procesoare 5x86 reprezinta o noua generatie pe 64 de biti compatibila x86. Unitatea centrala se bazeaza pe o banda de asamblare cu sase nivele, putand executa o instructiune intr-un impuls de tact.

Unitatea centrala 5x86 este divizata in urmatoarele blocuri functionale (Fig. 1): unitatea pentru numere intregi (Integer Unit - IU), unitatea in virgula flotanta (Floating Point Unit - FPU) , unitatea cache (Write-Back Cache) , unitatea pentru gestiunea memoriei (Memory Management Unit - MMU) , unitatea de interfata cu magistrala (Bus Interface Unit - BIU). Unitatea pentru numere intregi contine: tamponul pentru instructiuni (Instruction Buffer - IB) , unitatea de aducere a instructiunii (Instruction Fetch Unit - IF) , unitatea de decodificare a instructiunii (Instruction Decoder Unit - ID).

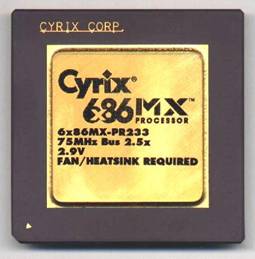

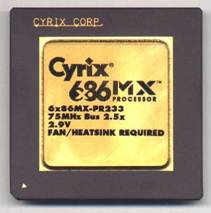

2.8 Cyrix

6x86MX (30 Mai 1997) 6x86MX a adus nou extensiile MMX

precum si viteze de ceas mai mari decat precedentele chip-uri de la Cyrix.

Astfel cel mai performant model era 6x86MX

PR266 care rula la 233MHz. De asemenea, marimea memoriei cache Level2

s-a marit de patru ori fata de 6x86, ajungand la 64Kb.

2.8 Cyrix

6x86MX (30 Mai 1997) 6x86MX a adus nou extensiile MMX

precum si viteze de ceas mai mari decat precedentele chip-uri de la Cyrix.

Astfel cel mai performant model era 6x86MX

PR266 care rula la 233MHz. De asemenea, marimea memoriei cache Level2

s-a marit de patru ori fata de 6x86, ajungand la 64Kb.

|

Arhitectura x86

Corporatia Cyrix este unul dintre furnizorii de baza ai solutiilor bazate pe microprocesoare, care a introdus noi standarde pe piata calculatoarelor personale. In ultimii zece ani Cyrix a dezvoltat aproape o duzina de procesoare originale folosite in milioane de calculatoare din intreaga lume.

In luna noiembrie a anului 1997, Cyrix a fost cumparata de National Semiconductor. Aceasta fuziune a adus doua componente importante pentru Cyrix: capacitatea de productie la nivel mondial a National Semiconductor si infrastructura necesara acestei productii.

Primul produs Cyrix a fost un coprocesor matematic destinat cresterii vitezei de realizare a calculelor matematice. Succesul acestui coprocesor matematic a permis celor de la Cyrix sa distribuie incepand cu 1992, primul procesor din familia x86. Compania a dezvoltat rapid o linie de productie pentru procesoarele 486, si apoi pentru procesoarele din generatia a cincea 5x86, un CPU pentru sistemele PC (mobile si desktop). In 1995, Cyrix a introdus procesorul din generatia a sasea, 6x86, un procesor superscalar, bazat pe o superbanda de asamblare; in iunie 1997, a introdus procesorul MMX 6x86MX, iar in 1998 a aparut procesorul MII.

Principalele blocuri functionle

Procesorul Cyrix 6x86 contine cinci mari blocuri functionale: -Unitatea intreaga (Integer Unit - IU) , -Unitatea cache (Cache Unit) ,

-Unitatea de gestionare a memoriei (Memory Management Unit - MMU) , -Unitatea in virgula flotanta (Floating Point Unit - FPU) , -Unitatea de interfata cu magistrala (Bus Interface Unit - BIU).

Instructiunile sunt executate in cele doua benzi de asamblare intregi (X si Y) si in unitatea in virgula flotanta. Cache-ul contine cele mai recent utilizate date si instructiuni pentru a permite accese rapide la informatii din partea IU si FPU.

Adresele fizice sunt calculate de MMU si sunt trimise unitatii cache si unitatii de interfata cu magistrala. BIU ofera o interfata intre placa sistem externa si unitatile interne ale procesorului.

Unitatea intreaga

Unitatea de calcul cu numere intregi ofera o executie paralela a instructiunilor in doua benzi de asamblare pentru numere intregi cu sapte nivele. Fiecare din cele doua benzi de asamblare (X si Y) poate procesa simultan cateva instructiuni.

Unitatea cache

Procesorul Cyrix 6x86 contine un cache unificat pentru date si instructiuni de 16Ko, set-asociativ pe patru cai, organizat pe 1055 de linii. Scrierile in cache se fac prin metoda write-back. Memoria cache este organizata in patru bancuri a cate 256 linii fiecare, cu 16 octeti pe linie. Fiecare linie cache are asociat cate un tag pe 21 de biti si un bit de valid

(arata daca linia contine informatii valide sau nu). Pe langa acesti biti, fiecare linie mai contine inca patru biti care indica daca continutul liniei a fost

modificat (dirty bits), cate unul pentru fiecare dublu-cuvant din linie. Acesti ultimi patru biti permit marcarea independenta a fiecarui dublu-cuvant ca fiind modificat, in loc de a marca intreaga.

Unitatea de gestionare a memoriei

MMU translateaza adresele liniare furnizate de IU in adrese fizice, pentru a putea fi folosite de unitatea cache si unitatea de interfata cu magistrala. Mecanismul de paginare este cel standard x86.

Unitatea pentru gestionarea memoriei mai contine un bloc (Load/Store Unit) care planifica accesele la memoria cache si memoria externa si implementeaza urmatoarele concepte: -reordonarea citirilor si scrierilor - confera o prioritate mai mare citirilor din memorie fata de scrierile in memorie, -evitarea citirilor din memorie - elimina citirile inutile din memorie prin folosirea datelor existente deja in unitatea centrala (in cazul dependentelor de tipul citire dupa scriere).

Controlul ramificatiilor, prezicerea ramificatiilor, dependentele intre date, unitatea in virgula flotanta, unitatea de interfata cu magistrala vor fi prezentate la procesorul 6x86.

2.11 Principalele imbunatatiri fata de 5x86

Procesarea in ordine

Daca o instructiune este executata mai repede decat instructiunea precedenta din cealalta banda de asamblare, instructiunile sunt completate in inordine.

Toate instructiunile sunt prelucrate in ordine pana la nivelul EX. In timp ce in nivelele EX si WB instructiunile pot fi executate in inordine.

Daca exista dependente de date intre cele doua instructiuni, este necesara interventia unui bloc care sa asigure executia corecta a programului. Astfel, chiar daca instructiunile sunt executate in inordine, exceptiile si scrierile din cadrul instructiunilor sunt intotdeauna efectuate in ordinea ceruta de program.

Selectarea benzii de executie

In majoritatea cazurilor, instructiunile sunt prelucrate in oricare din cele doua benzi de asamblare si nu exista constrangeri cu privire la tipul instructiunilor executabile in paralel in cele doua benzi de asamblare. Insa, unele instructiuni pot fi prelucrate doar de banda de asamblare X: -instructiunile de salt, -instructiunile in virgula flotanta, -instructiunile exclusive.

Instructiunile de salt si cele in virgula flotanta pot fi executate in paralel cu o alta instructiune ce poate fi executata in banda Y. Instructiunile exclusive nu

pot fi executate in paralel cu nici o alta instructiune. Aceste instructiuni necesita accese multiple la memorie. Chiar daca aceste instructiuni sunt

executate exclusiv, este folosit hardware-ul din cele doua benzi de asamblare pentru a se accelera completarea instructiunii. In continuare sunt insirate

tipurile de instructiuni exclusive ale procesorului 6x86: -incarcarea segmentelor in modul protejat, -accesele la registrele speciale (registrele de control, debug si test) , -instructiunile pe siruri, -inmultirea si impartirea,

accesele la porturile I/O, -PUSHA si POPA, -salturile intersegment, apelurile de proceduri si iesirea din proceduri intersegment.

Solutionarea dependentelor de date

Cand doua instructiuni care sunt executate in paralel acceseaza aceeasi data sau acelasi registru, poate apare una din urmatoarele tipuri de dependente de date: -citire dupa scriere (Read-After-Write - RAW) , -scriere dupa citire (Write-After-Read - WAR) , -scriere dupa scriere (Write-After-Write - WAW).

Dependentele intre date in mod normal necesita serializarea executiei instructiunilor implicate. Insa, 6x86 implementeaza urmatoarele trei mecanisme ce permit executia paralela a instructiunilor ce contin dependente intre date: -redenumirea registrelor (Register Renaming) , -inaintarea datelor (Data Forwarding) , -evitarea datelor (Data Bypassing). In continuare, se vor descrie pe scurt aceste meacnisme. Procesorul Cyrix 6x86 contine 32 registre fizice de uz general. Fiecare din cele 32 de registre din fisierul de registre poate fi desemnat a fi unul din registrele de uz general din arhitectura x86 (EAX, EBX, ECX, EDX, ESI, EDI, EBP si ESP). Pentru fiecare operatie de scriere intr-un registru este selectat un nou registru fizic, pentru a se retine

temporar si data precedenta. Redenumirea registrelor elimina efectiv toate dependintele WAW si WAR. Pentru programator este transparent acest mod de redenumire a registrelor; este transparent atat pentru sistemul de operare, cat si pentru programele aplicatie.

Inaintarea datelor (Data Forwarding)

Doar redenumirea registrelor, nu poate elimina dependentele de tipul citire dupa scriere (RAW). 6x86 foloseste doua tipuri de data forwarding impreuna cu redenumirea registrelor pentru a elimina acest tip de

dependente: -inaintarea operandului (operand forwarding), - apare cand prima dintr-o pereche de instructiuni efectueaza o citire din registru sau memorie iar aceasta data este necesara celei de-a doua instructiuni. CPU executa operatia de citire si furnizeaza data citita ambelor instructiuni; -inaintarea rezultatului (result forwarding) - apare atunci cand prima dintr-o pereche de instructiuni executa o operatie (cum ar fi ADD) iar rezultatul ei este citit de o a doua instructiune. CPU-ul executa operatia primei instructiuni si depune rezultatul operatiei in destinatiile ambelor instructiuni simultan.

Evitarea datelor (Data Bypassing)

Pe langa redenumirea registrelor si inaintarea datelor, 6x86 contine o a treia tehnica de eliminare a dependentelor de date, denumita evitarea datelor. Aceasta reduce scaderilor in performanta ale acelor dependente de tipul RAW din memorie ce nu pot fi eliminate cu ajutorul inaintarii datelor.

Evitarea datelor apare cand prima dintr-o pereche de instructiuni scrie in memorie si urmatoarea citeste aceeasi data din memorie. 6x86 retine data din

prima instructiune si o paseaza celeilalte instructiuni, astfel eliminandu-se un ciclu de citire din memorie.

Prezicerea salturilor

Procesorul 6x86 foloseste un tabel al adreselor destinatie (Branch Target Buffer - BTB) cu 256 de intrari, set asociativ pe 4 cai, pentru mentinerea adreselor destinatie ale instructiunile de salt si a altor informatii necesare prezicerii acestor salturi. In timpul aducerii codului instructiunii sunt

cautate instructiunile de salt in fluxul de instructiuni. Daca este descoperita o instructiune de salt neconditionat, CPU-ul acceseaza BTB pentru a afla adresa destinatie a instructiunii de salt. Daca aceasta adresa exista in BTB, CPU-ul incepe sa aduca instructiunile de la noua adresa.

In cazul salturilor conditionate, BTB mai mentine o serie de informatii cu privire la istoricul efectuarii saltului respectiv (pentru a se putea lua decizia de efectuare sau nu a saltului). Daca instructiunea de salt conditionat este gasita in BTB, 6x86 incepe aducerea instructiunilor de la adresa prezisa. Daca instructiunea nu este gasita in BTB, 6x86 prezice neexecutarea saltului si aducerea instructiunilor va continua cu adresa urmatoare. Decizia de efectuare sau nu a saltului este luata pe baza unui algoritm de prezicere a salturilor.

Odata ce a fost adus codul unei instructiuni de salt conditionat, aceasta este decodificata si distribuita spre executie benzii de asamblare X. Instructiunea trece prin nivelele benzii de asamblare X si este terminata sau in nivelul EX sau in WB, in functie de instructiunea care a setat indicatorii de

conditii: -daca instructiunea care a setat indicatorii de conditii este executata in paralel cu instructiunea de salt conditionat, atunci aceasta este terminata in

nivelul WB, -daca instructiunea care a setat indicatorii de conditii a fost executata inaintea instructiunii de salt, atunci aceasta se va termina in EX.

Instructiunile de salt conditionat corect prezise se vor executa intr-un singur impuls de tact. Daca dupa terminarea executiei instructiunii de salt conditionat s-a detectat o prezicere eronata a saltului, CPU-ul goleste benzile de asamblare si incepe executia de la adresa corecta. Procesorul 6x86 in cazul unei instructiuni de salt conditionat aduce in avans atat instructiunea prezisa cat si cealalta, dar o trimite benzii de asamblare spre executie doar pe cea prezisa. Astfel ca, in cazul unei preziceri eronate, instructiunea de la adresa neprezisa nu va mai fi citita din cache, deoarece a fost adusa deja. Daca instructiunea de salt conditionat a fost rezolvata in nivelul EX, atunci intarzierea in cazul unei preziceri eronate este de patru impulsuri de tact, iar daca instructiunea de salt a fost rezolvata doar in WB, atunci intarzierea este de cinci impulsuri de tact.

Deoarece instructiunea de revenire dintr-o subrutina (RET) este dinamica, procesorul 6x86 mentine adresele pentru aceste instructiuni intr-o stiva cu opt intrari. Adresa de revenire este introdusa in stiva adreselor de revenire de catre instructiunea CALL, si este scoasa de catre instructiunea RET corespunzatoare.

Executia speculativa

Procesorul 6x86 are posibilitatea de a executa speculativ instructiunile urmatoare unei instructiuni in virgula flotanta sau a unei instructiuni de salt.

Executia speculativa permite benzilor de asamblare sa execute continu instructiuni dupa un salt, fara a fi necesara blocarea benzii de asamblare pana la obtinerea rezultatului executiei instructiunii de salt conditionat. Acelasi

mecanism este folosit pentru a se executa instructiuni in virgula flotanta in paralel cu instructiunile de numere intregi.

Procesorul are posibilitatea de executie in patru nivele de speculatie. Dupa generarea unei noi adrese prin mecanismul de predictie, CPU-ul salveaza starea curenta (registrele, indicatorii de conditii, etc.), incrementeaza numaratorul nivelului de speculatie si incepe executia fluxului de instructiuni prezis.

Odata ce instructiunea de salt a fost rezolvata, CPU-ul decrementeaza nivelul de speculatie. Pentru un salt corect prezis este stearsa starea resurselor salvate la intrarea in nivelul de speculatie curent. Pentru un salt prezis eronat, procesorul 6x86 genereaza adresa corecta pentru urmatoarea instructiune si foloseste valorile de stare salvate pentru a restaura starea curenta, intr-un singur impuls de tact.

Pentru a se mentine compatibilitatea, nu sunt permise scrierile in memorie sau cache, pana cand nu este rezolvata instructiunea de salt. Executia speculativa continua pana cand apare una din urmatoarele conditii: -este decodificata o noua instructiune de salt sau de calcul in virgula flotanta si nivelul de speculatie este patru (maximul) , -apare o exceptie sau o eroare, -tamponul de scriere este plin, -se incearca modificarea unei resurse a carei stare nu a fost salvata (registrele segment, indicatorii sistem).

Mecanismul de paginare cu dimensiunea paginilor variabila

Acest mecanism de paginare permite programelor sa mapeze pagini cu dimensiunea intre 4Ko si 4Go. Folosirea paginilor de dimensiuni mari poate duce la sporirea performantei unor anumite aplicatii.

Mecanismul traditional de paginare

Mecanismul traditional de paginare a fost imbunatatit la 6x86 prin adaugarea unui cache pentru tabelul directorilor (Directory Table Entry -DTE) si un TLB victima. TLB-ul principal este cu mapare directa si contine 128 de intrari pentru tabelul paginilor. Cache-ul DTE cu patru intrari complet asociative contine accesele cele mai recente la DTE.

TLB-ul victima contine liniile din TLB principal care au fost inlocuite datorita unui miss in TLB. Daca se face referirea la o pagina ce are PTE-ul in TLB-ul victima, linia aceasta este schimbata cu o linie din TLB-ul primar.

Unitatea in virgula flotanta

Interfata dintre unitatea in virgula flotanta (FPU) a procesorului 6x86 si unitatea pentru numere intregi este realizata printr-o magistrala interna pe 64 de biti. Setul de instructiuni FPU al procesorului 6x86 este compatibil x87 si adera standardului IEEE-754.

Procesorul Cyrix 6x86 executa instructiunile intregi in paralel cu instructiunile in virgula flotanta. Instructiunile intregi pot fi executate in inordine cu respectarea instructiunilor FPU.

Asa cum s-a mai spus, instructiunile FPU sunt intotdeauna executate in banda de asamblare X. Nivelul pentru calculul adresei din banda X verifica aparitia exceptiilor de gestionare a memoriei si acceseaza operanzii din memorie folositi de FPU. Daca nu apare nici o exceptie, se salveaza starea curenta a procesorului in AC2 si trimite instructiunea in virgula flotanta spre

executie FPU-ului. Apoi unitatea centrala poate executa orice instructiune intreaga urmatoare, speculativ si in inordine.

Unitatea centrala 6x86 poate trimite pana la patru instructiuni FPU in coada de asteptare a FPU. CPU-ul continua cu executia speculativa si in inordine pana cand apare una dintre conditiile ce cauzeaza oprirea executiei speculative. Pe masura ce FPU termina de executat o instructiune in virgula flotanta, este decrementat nivelul speculativ si sunt sterse valorile de stare salvate la inceputul acestei instructiuni. Unitatea in virgula flotanta mai

contine si un set de patru tampoane de scriere pentru a preveni intreruperile datorate scrierilor speculative.

Cyrix MediaGX

MediaGX a reprezentat incercarea lui Cyrix de a produce un chip care sa integreze atat functiile de sunet si video, cat si controller-ul de memorie si CPU-ul in sine. Scopul acestui chip a fost acela de a putea produce

computere foarte ieftine si la vremea aceea deja se vorbea de calculatoare sub 500$ construite in jurul lui MediaGX. Cu toate acestea, nici unul din marii producatori de computere nu a adoptat aceasta solutie, astfel incat procesorul acesta, desi revolutionar, nu a avut deloc succesul scontat.

2.13 Intel Pentium II (1997)

Urmatorul procesor de la Intel, dupa Pentium, s-a numit Pentium II. Acesta folosea un nou design si avea nevoie de placi de baza noi, bazate pe slot 1(procesorul se afla, impreuna cu memoria cache Level2, pe o placuta care se introducea intr-un slot special). Vitezele atinse de acest procesor s-au situat intre 233 si 450MHz. Spre deosebire de PentiumPro, memoria cache Level 2 nu rula la intreaga viteza a frecventei procesorului ci numai la jumatate din aceasta.

2.14 Intel Pentium II Xeon (1998)

Echivalentul Pentium II construit insa pentru servere s-a numit Pentium II Xeon. Acesta era o varianta usor modificata a lui Pentium II, dispunand insa de un cache Level2 integrat de pana la 2MB. Aceasta cantitate impresionanta a memoriei cache dus insa si la preturi de vanzare foarte mari, un Pentium II Xeon fiind de 2-3 ori mai scump decat un Pentium II la aceeasi frecventa.

2.15 Intel Celeron (1998)

Dupa ce lansase procesoare atat pentru statii de lucru (Pentium II) cat si pentru servere (Pentium II Xeon) a venit si timpul unei solutii foarte ieftine pentru calculatoarele de acasa. Aceasta solutie s-a numit Celeron care era de fapt o versiune de Pentium II care folosea o magistrala de doar 66MHz si nu dispunea de cache Level2. Aceste doua 'gatuiri' in arhitectura noului procesor au reprezentat un mare dezavantaj, in comparatie cu alte microprocesoare. Aceasta versiune de Celeron a avut viteze intre 266 si 366MHz.

2.16 AMD K6/2 (1998)

Una din cele mai interesante noutati aduse de K6/2 a fost introducerea unui nou set de instructiuni folositoare in aplicatiile 3D, pe care AMD l-a denumit 3DNow! Acest procesor a insemnat inceputul revirimentului companiei AMD deoarece K6/2 se putea lupta de la egal la egal cu procesoarele Intel ale perioadei respective. In plus, aplicatiile si jocurile cu suport pentru extensiile 3DNow! beneficiau de un spor de viteza considerabil. Din pacate, executia instructiunilor in virgula mobila a continuat sa fie punctul

slab al procesoarelor de la AMD. K6/2 a rulat la viteze intre 266 si 550MHz.

magistrale de 133Mhz.

2.17 AMD Duron (2000)

In anul 2000 AMD detinea deja procesoare cel putin la fel de rapide cu cele mai bune procesoare de la Intel. Era momentul ca AMD sa-si intareasca si pozitia sa pe piata low-end pe care a activat cu succes pana acum. Pentru aceasta, a lansat procesorul AMD Duron. Spre deosebire de Celeron care era gatuit de o magistrala de date de doar 66Mhz, Duron functiona pe acelasi tip de magistrala ca si Athlon Thunderbird. Singura deosebire o reprezinta marimea cache-ului Level2: 64Kb fata de 256Kb la Thunderbird. Cu toate acestea Duron este doar cu aproximativ 5-10% mai lent in majoritatea

cazurilor decat Thunderbird. Aceasta, ca si pretul sau foarte convenabil au

facut din acest procesor unul din cele mai cautate pe piata calculatoarelor pentru acasa. Vitezele AMD Duron variaza intre 600 si 1100MHz.

2.18 AMD Athlon (1999)

Procesorul care a readus cu adevarat compania AMD in prim-plan a fost Athlon (sau K7 cum a mai fost cunoscut). Acesta reuseste sa lupte de la egal la egal si chiar sa depaseasca in anumite situatii procesoarele similare de la Intel, toate acestea la preturi de multe ori la jumatate din cele ale concurentului direct. Dupa cum si Pentium II a fost construit initial folosind un design nou bazat pe slot, la fel si Athlon a necesitat placi de baza noi construite in jurul Slot A. Un mare dezavantaj al acestor procesoare a fost totusi faptul ca din cauza frecventelor ridicate de functionare (intre 500MHz si 1GHz) consuma foarte mult curent si degaja ca urmare multa caldura.

2.19 Intel Pentium III (1999)

Pentium III a adus ca noutate absoluta un nou set de instructiuni

multimedia (70 de instructiuni noi) concepute special pentru aplicatiile 3D pe care le-a denumit SSE. Procesorul functiona tot pe placi de baza construite pe baza Slot 1, si avea integrat 512Kb memorie cache Level2. Aceasta prima varianta de Pentium III a fost cunoscuta si sub numele de Pentium III Katmai. Ulterior, Intel si-a dat seama ca Slot1 nu este necesar si a hotarat ca toate procesoarele noi Pentium III sa fie construite pe Socket 370 asemanatoare cu cea folosita la Pentium. De asemenea, odata cu aceasta schimbare, memoria cache Level 2 a fost adusa la aceeasi frecventa cu cea a procesorului, marimea ei scazand insa la 256 Kb. Pentru a facilita aceasta schimbare a designului precum si pentru a obtine frecvente de functionare mai mari si pentru a micsora caldura degajata, Intel a trecut la un proces de fabricatie de 0,18 microni. Numele de cod al noii versiuni de Pentium III a fost Coppermine. Pentru a putea fi identificate mai usor aceste noi procesoare au primit litera E imediat dupa valoarea frecventei. De exemplu: Pentium III 667E MHz. O alta imbunatatire a performantelor a fost adusa de folosirea unei magistrale au primit in plus litera B (Pentium III 733EB MHz). Vitezele atinse de Pentium III s-au situat intre 450MHz si 1GHz.

2.20 Intel Pentium 4 (2000)

Pentium IV cunoscut si sub numele de cod Willamette, este cel mai nou model al familiei de microprocesoare Intel pe 32 de biti, care lucreaza la frecvente mai mari si inregistreaza performante superioare fata de modelele precedente.

Noua microarhitectura a acestor procesoare a fost denumita de catre Intel, NetBurst, in spatele acestei tehnologii aflandu-se urmatoarele noi facilitati: busul sistemului la 400MHz - utilizand noua tehnologie ,quad pumped' cu o latime a magistralei de 64 biti si ceas de 100MHz, se ajunge la o rata de transfer intre procesor si memorie de 3200 MB/s, de 3 ori mai mare ca cea a procesoarelor Pentium III. Pentium III putea transfera doar 1.06G la o frecventa de 133MHz. Pentium IV

lucreaza prin intermediul a doua canale de transmisie cu RDRAM, la o viteza de 3.2G/s.

CONCLUZII

Am vazut in acest articol ca performanta microprocesoarelor s-a situat pe o curba exponentiala in toti cei treizeci de ani de la crearea lor. Am vazut ca miniaturizarea si tehnicile de design contribuie in mod egal la aceste spectaculoase cresteri. De asemenea, am vazut ca cresterea aceasta se apropie de sfarsit, datorita unor bariere fizice fundamentale. In fine, am

incercat sa profetim unele din tehnologiile care-si vor face aparitia in generatiile urmatoare de procesoare

4.PROTECTIA MUNCII

Protectia muncii este un ansamblu de masuri tehnice, sanitare si organizatorice, avand ca scop ocrotirea vietii si sanatatii, celor care muncesc.

Spre deosebire de cele mai multe tipuri de instalatii la care pericolele posibile sunt sesizate de simturile omenesti, la instalatiile electrice tensiunea

electrica nu poate fi sesizata, pentru ca omul sa poata fi prevenit asupra posibilelor pericole.

In cazul in care omul atinge simultan doua corpuri bune conducatoare de electricitate intre intre care exista o diferenta de potential electric de exemplu dupa conductoare electrice neizolate, corpul sau va fi strabatut de un curent electric, accident care se numeste electrocutare.

Electrocutarea poate avea loc prin atingerea directa a partilor din circuitele electrice sau prin atingerea indirecta, adica atingerea unei parti metalice care nu face parte din circuitul electric dar este pus accidental sub tensiune.

Tensiunea la care este supus omul la atingerea unui obiect intrat accidental sub tensiune este numita tensiune de atingere.

Efectele trecerii curentului electric prin corpul omului sunt: socul electric si electrotraumatismele.

Factorii de care depinde gravitatea electrocutarii sunt

rezistenta electrica a corpului uman

calea de trecere a curentului prin corp

tensiunea la care este supus omul

frecventa curentului electric.

Protectia impotriva electrocutarii

La alegerea masurilor pentru protectia impotriva electrocutarii, se au in vedere caracteristicile locurilor de munca, acestea clasificandu-se in trei categorii, in functie de gradul de pericol:

locuri de munca foarte periculoase

locuri de munca periculoase

locuri de munca cu grad mic de pericol

Protectia impotriva electrocutarii se face in functie de modul de atingere: directa sau indirecta.

Principalele masuri pentru evitarea electrocutarilor prin atingere involuntara sunt:

-proiectarea si construirea instalalatiilor si echipamentelor electrice astfel incat elementele aflate normal sub tensiune sa nu poata fi atinse intamlator.

-folosirea unor pardoseli din materiale izolate

-folosirea unor tensiuni reduse

Principalele masuri pentru evitarea electrocutarilor prin atingere directa sunt:

●legarea la nul

●legarea la pamant

●separarea de protectie

●izolarea suplimentara de protectie

●folosirea tensiunilor reduse

●protectia prin deconectarea automata

5. BIBLIOGRFIE

1- Tamas Nastase, Ionescu Berbec, Cosacescu Ionescu Oanxcea -Bazele informaticii editura Sofitek 1999

2- Carstea Mihaela, Ioan Diamanti -Calculatorul fara secrete editura Agni Bucuresti 1997

3- Dodescu Gheorghe, Marsanu Radu, Nastase Florea- Calculatoare.element fundamental de strict.initiere in utilizarea pc-ului editura ALL 2000

4- www.muntealb.com/manual 5-www.hp.com.ro/istorie 6-Lector universitar doctor Cezar Botezatu- Arhitectura calculatoarelor personale si sisteme de operare specifice editura Universul juridic 2005

7-bwrc.eecs.berkeley.edu/CIC/archive/ cpu_history.html.

8-www.clopotel.ro

9- www.referate.ro

| Contact |- ia legatura cu noi -| | |

| Adauga document |- pune-ti documente online -| | |

| Termeni & conditii de utilizare |- politica de cookies si de confidentialitate -| | |

| Copyright © |- 2025 - Toate drepturile rezervate -| |

|

|

||||||||||||||||||||||||

|

||||||||||||||||||||||||

|

||||||||||||||||||||||||

Referate pe aceeasi tema | ||||||||||||||||||||||||

|

| ||||||||||||||||||||||||

|

||||||||||||||||||||||||

|

|

||||||||||||||||||||||||