| Afaceri | Agricultura | Comunicare | Constructii | Contabilitate | Contracte |

| Economie | Finante | Management | Marketing | Transporturi |

Electrica

|

|

Qdidactic » bani & cariera » constructii » electrica aplicatii de electronica analogica si digitala -area detectoarelor de varfarea multiplicatorului logaritmic, propunere de cablaj imprimat |

aplicatii de electronica analogica si digitala -area detectoarelor de varfarea multiplicatorului logaritmic, propunere de cablaj imprimat

Introducere

Tema proiectului

Sa se proiecteze un sistem analogic care sa realizeze produsul valorilor efective a doua marimi pur sinusoidale.

Sistemul analogic se implementeaza cu amplificatoare operationale (AO) si un multiplicator logaritmic.

Produsul semnalelor se face cu un multiplicator analogic ( de tip logaritmic).

Datele de proiectare

Sistemul analogic se proiecteaza pe baza urmatoarelor date:

Amplitudinea (valoarea

de varf) primului semnal: ![]() = 5.2 V;

= 5.2 V;

Amplitudinea celui de

al doilea semnal: ![]() = 2.8 V;

= 2.8 V;

Rezistenta

minima de intrare pentru fiecare semnal: ![]() = 900 MW

= 900 MW

Domeniul de frecventa al semnalelor:

Frecventa

limita inferioara: ![]() = 50 Hz;

= 50 Hz;

Frecventa

limita superioara: ![]() = 12KHz;

= 12KHz;

Eroarea impusa:

![]() =

1.6%;

=

1.6%;

Alimentarea

sistemului: ![]() .

.

Schema bloc a sistemului analogic

Multiplicatorul logaritmic are in structura sa 3 circuite de logaritmare si un circuit de exponentiere. Multiplicatorul are 3 intrari si o iesire (fig. 1) si poate fi configurat astfel:

Pentru inmultire daca V3=const.;

Pentru impartire daca V1=const. sau V2=const.;

Pentru operatie complexa de inmultire si impartire, daca pe toate cele 3 intrari se aplica semnale.

Fig. 1. Schema bloc a multiplicatorului logaritmic

Circuitele de logaritmare si exponentiere lucreaza numai cu semnale de o singura polaritate. Din aceasta cauza, la intrarile multiplicatorului logaritmic trebuie sa se conecteze circuite redresoare. Sistemul analogic fiind un circuit de masurare, redresoarele trebuie sa fie de tipul redresoare de precizie.

Din semnalul sinusoidal

![]()

unde U

reprezinta valoarea efectiva, utilizand un redresor de precizie

monoalternanta, urmat de un condensator de filtrare, se poate

obtine o tensiune continua egala cu valoarea de varf ![]() . De aceea acest redresor se numeste detector

de varf.

. De aceea acest redresor se numeste detector

de varf.

Produsul valorilor efective a doua semnale sinusoidale se poate scrie in functie de amplitudinile semnalelor:

Rezulta:

![]() ,

,

![]() si

si

![]() .

Schema bloc a sistemului analogic se prezinta in fig. 2.

.

Schema bloc a sistemului analogic se prezinta in fig. 2.

Fig. 2. Schema bloc a sistemului analogic

Pentru ca tensiunile de intrare sunt in curent alternativ introducerea lor in blocul multiplicator se va face prin circuite detectoare de varf.

Proiectarea detectoarelor de varf

Detectoarele de masurare se folosesc pentru a transforma semnalul variabil in timp intr- un semnal constant( tensiune sau curent electric). Astfel, semnalele continue pot fi prelucrate de catre multiplicatorul logaritmic.

Detectoarele de varf in electronica se mai numesc si demodulatoare in amplitudine.( [6])

Tipuri de detectoare :

- Detector de valori de varf cu amplificator operational

Detector de valori medii absolute cu amplificator operational

Detector de valoare efectiva cu amplificator operational (RMS)

Conversia curent alternativ curent continuu

Pentru conversia tensiunilor alternative de frecvente relativ joase (max. sute de kHz) se folosesc: detectoare de precizie pentru valoarea medie redresata,convertoare de valoare efectiva. Detectoarele de precizie dau la iesire o tensiune continua, egala cu valoarea medie redresata a semnalului de intrare. Indicatiile multimetrului sunt valabile numai in regim sinusoidal, ceea ce constituie o limitare majora a acestui tip de conversie. Avantajul principal il constituie precizia ridicata (pana la 0,01 %).

Convertorul pentru valoarea efectiva (sau convertor RMS root mean square = radacina medie patratica)

Are o raspandire larga, datorita posibilitatii utilizarii lui si in regim nesinusoidal, cat si simplitatii lui si realizarii pe cale integrata.

Alegerea schemei

Alegerea schemei se face in concordanta cu functia de transfer a circuitului, impusa prin datele de proiectare.Valoarea impedantei de intrare poate fi critica. Valoarea impedantei de intare avand valori de ordinul Megaohmilor, trebuie sa se foloseasca configuratia neinversoare a amplificatorului operational. .( [2])

Valoarea tensiunii continue este data de valoarea maxima a semnalului sinusoidal. Aceasta valoare se mentine datorita unui condensator care se incarca la valoarea de varf pana cand se atinge o noua valoare de varf a tensiunii de intrare. Valoarea maxima in modul a semnalului este aceeasi pentru ambele alternante. Astfel este suficienta o redresare monoalternanta.( [1])

Deoarece rezistenta de intrare a sistemului este mare, se alege un redresor de precizie monoalternenta de tip neinversor. Pentru a evita saturarea AO, se utilizeaza dioda suplimentara D2 (la fel ca la redresorul inversor). Rezulta schema din fig. 3.

Fig. 3.

Rezistenta RF asigura curentul minim prin dioda D1.

Schema prezinta urmatorul dezavantaj: in timpul alternantei negative a tensiunii de intrare uin, condensatorul de filtrare CF se descarca prin D2 la sursa negativa, asa cum arata sagetile de pe fig. 3. Pentru a evita acest dezavantaj, la iesirea circuitului din fig. 3 se conecteaza un buffer analogic (circuit repetor neinversor). Reactia trebuie izolata de restul circuitului.

Rezulta circuitul din fig. 4.

Fig. 4. Schema detectorului de varf

Detectorul de varf determina si rezistenta de intrare a circuitului care trebuie sa fie foarte mare.

Tensiunea de intrare are o frecveta superioara ce influenteaza nivelul de semnal (care in cazul nostru este de nivelul voltilor). Amplificarea scade o data cu scaderea frecventei.( [1])

Elementele de baza ale detectorului de varf sunt:

memoria analogica, realizata de un condensatorul CF

dioda care permite incarcarea condensatorului la valoarea de varf a tensiunii de intrare

un repetor de tensiune (X2)

RF este necesara pentru a asigura curentul minim de deschidere al diodei D1

Alegerea AO

Indiferent de tipul circuitului cu reactie negativa realizat cu AO, rezistenta de iesire este mica, ceea ce permite cuplarea comoda in cascada a circuitelor, fara sa aiba loc pierderi de semnal prin divizarea acestuia intre rezistenta de iesire a circuitului si cea de intrare a circuitului urmator.( [2])

Pentru alegerea AO se utilizeaza urmatoarele criterii:

Criteriul SR

AO corespunde din punct de vedere al vitezei de variatie maxime a semnalului de iesire daca:

![]()

unde

fS reprezinta frecventa limita superioara (valoarea maxima a frecventei semnalelor prelucrate);

![]() este amplificarea in bucla inchisa, in

modul;

este amplificarea in bucla inchisa, in

modul;

![]() - amplitudinea (valoarea de varf) a semnalului de

intrare prelucrat.

- amplitudinea (valoarea de varf) a semnalului de

intrare prelucrat.

![]() =max= max= 5.2V

=max= max= 5.2V

![]() =1 T

=1 T

![]() 0.392V/ms

0.392V/ms

Criteriul abaterii amplificarii reale in bucla inchisa

Conform acestui criteriu, AO corespunde daca amplificarea in bucla deschisa, la frecventa maxima (frecventa limita superioara fS) indeplineste relatia:

unde

eimp se transforma din procente in valoare absoluta

1/b reprezinta inversul factorului de reactie al circuitului cu AO.

1/b=1 ; eimp

T

T ![]()

AO se alege astfel incat valoarea amplificarii in bucla deschisa la fs sa permita determinarea amplificarii in bucla inchisa cu o eroare mai mica decat cea impusa in datele de proiectare.([2])

Criteriul rezistentei de intrare

AO ales corespunde din punctul de vedere al acestui criteriu daca rezistenta de intrare diferentiala a AO satisface relatia:

![]()

unde amplificarea la frecventa limita superioara a(fS) are valoarea determinata la criteriul anterior.

![]() =900MW T

=900MW T

![]() =137.9762MW T

=137.9762MW T ![]() 137.9762MW

137.9762MW

S- a ales utilizarea AO cu JFET la intrare, care, din descrierea generala este potential adecvat aplicatiei de fata.

Stabilitatea detectoarelor de varf

Pentru a determina stabilitatea detectoarelor de varf, se extrag urmatoarele date:

Valoarea maxima a amplificarii in bucla deschisa;

Frecventele

polilor (fp1 si fp2).

Daca fp2 nu este precizat, se poate alege

valoarea ![]() ;

;

Valoarea produsului amplificare-banda, PAB.

Analiza stabilitatii cu ajutorul caracteristicilor Bode se face astfel:

cunoscand din catalog frecventele polilor AO pentru functia de transfer a amplificarii in bucla deschisa, se deseneaza caracteristica de amplitudine, la care:

fiecare pol frange caracteristica de amplitudine cu -20dB/dec;

fiecare zero frange caracteristica de amplitudine cu +20dB/dec;

din analiza circuitului se determina expresia factorului de reactie b(f), daca este dependent de frecventa sau simplu b, daca factorul de reactie este real (independent de frecventa);

pe caracteristica de amplitudine se reprezinta inversul factorului de reactie, 1/b(f) sau 1/b si se pune in evidenta frecventa fo la care caracteristica de amplitudine, a(f), se intersecteaza cu 1/b(f) sau 1/b;

sub caracteristica de

amplitudine, se deseneaza caracteristicile de faza ja (dependenta de frecventa a fazei amplificarii in

bucla deschisa) si j1/b (dependenta de frecventa a

inversului factorului de reactie) daca factorul de reactie este

dependent de frecventa si apoi caracteristica rezultanta ![]()

curba (-j1/b se deseneaza ca imaginea in oglinda (fata de axa frecventelor) a curbei j1/b

daca factorul de reactie este independent de frecventa, este suficient sa se deseneze caracteristica ja

fiecare pol frange caracteristica de faza cu -45 /dec, incepand de la o frecventa de 10 ori mai mica decat cea corespunzatoare polului, avand faza la frecventa polului egala cu -45

la o frecventa de 10 ori mai mare decat cea corespunzatoare polului, faza devine egala cu -90 si ramane la aceasta valoare pentru cresterea in continuare a frecventei;

fiecare zero frange caracteristica de faza cu +45 /dec, incepand de la o frecventa de 10 ori mai mica decat cea corespunzatoare zeroului, avand faza la frecventa zeroului egala cu +45

la o frecventa de 10 ori mai mare decat cea corespunzatoare zeroului, faza devine egala cu +90 si ramane la aceasta valoare pentru cresterea in continuare a frecventei;

la frecventa fo de intersectie dintre curbele a(f) si 1/b(f) se determina marginea de faza, mf:

![]()

daca mf>0, atunci circuitul este stabil si AO nu trebuie compensat in frecventa;

daca mf<0, circuitul analizat oscileaza si AO trebuie compensat;

pentru mf=0, la frecventa fo apar supracresteri in curba amplificarii in bucla inchisa ceea ce inseamna posibilitatea de oscilatie, deci instabilitate. De aceea in circuitele practice trebuie indeplinita conditia:

|

![]()

Datele de catalog ale amplificatorului operational ales:

Conform rezultatelor obtinute pentru SR, rezistenta diferentiala si amplificarea a(fs) s- a ales amplificatorul operational TL081/082/084. Aceste amplificatoare operationale au JFET la intrare, consum redus, polarizare si offset de curent mici, THD mic, impedanta de intrare mare, SR mare, protectie la scut circuit la iesire, compensat intern in frecventa.

Date caracteristice pentru AO TL081/082/084:

SR 8..13V/ms >0.39v/ms

Rezistenta de intrare, rd= 1012W >137.976MW

Castigul in tensiune la semnal mare a= 25000 . 200000

Tensiunea

maxima de alimentare:  18V

18V

Puterea maxima disipata intern:- 680mW- 8p (plastic)

- 680mW- 20p (flat plck)

- 680mW- 14p (plastic)

Tensiunea

diferentiala de intrare maxima:  30V

30V

Tensiunea

individuala de intrare maxima:  15V

15V

Tensiunea de offset la intrare UIO=3 . 6mV

Curentul de offset la intrare IIO= 5 . 100pA

Curentul de polarizare a intrarilor Ib= 30 . 200pA

Factorul de rejectie a surselor de alimentare, SVRR: 70 . 86dB

Factorul de rejectie a modului comun, CMRR= 70 . 86dB

Curentul de iesire: 25.000 . 200.000

Rezistenta de iesire, ro=220W

Excursia

tensiunii de iesire( saturatie):  12V pentru Rs

12V pentru Rs 10kW si

10kW si  15V alimentarea

15V alimentarea

Curentul de alimentare Icc=1.4 . 2.8mA/amplificator

Produsul amplificare banda, PAB= 3MHz

Frecventa polilor: fp1=15Hz ; Pentru ca in catalog nu se da frecventa polului 2, ea se considera fp2= 20 MHz

Din diagrama Bode a circuitului atasata proiectului rezulta faptul ca detectorul de varf este un circuit stabil, deoarece, analizandu- se marginea de faza pe diagrama Bode se observa ca aceasta are valoarea mf= 90o>45o. Rezulta din aceasta relatie ca detectorul de varf nu necesita compensare in frecventa.

Dimensionarea elementelor de circuit

Pentru detectorul de varf elementele care trebuie dimensionate sunt CF si RF.

Condensatorul de filtraj CF (fig. 4) se

dimensioneaza astfel incat constanta de timp ![]() sa indeplineasca conditia:

sa indeplineasca conditia:

![]()

unde ![]() J=1/fJ

=

J=1/fJ

=![]() =0.02 reprezinta

perioada semnalului pentru frecventa limita inferioara.

=0.02 reprezinta

perioada semnalului pentru frecventa limita inferioara.

Daca RF are valori mari (zeci de kW), pentru CF rezulta valori mai mici, ceea ce inseamna piese de dimensiuni mici.

Se poate alege ([2], anexa 1)

![]()

Rezulta pentru CF (valoare standard din [2], anexa 2)

![]() =0.0002F=2mF

=0.0002F=2mF

T![]() mF

mF![]() 00kW=0.2s

00kW=0.2s

dar ![]() T

10 TJ= 10

T

10 TJ= 10![]() .02= 0.2sT

20s

.02= 0.2sT

20s![]() 0.2s ( relatie indeplinita) T dimensionarea a fost efectuata corect.

0.2s ( relatie indeplinita) T dimensionarea a fost efectuata corect.

Rezistorul R asigura functionarea circuitului ca detector de varf. In absenta lui R, semnalul de iesire arata ca cel de la iesirea unui redresor monoalternanta, fara filtru. Valoarea lui R se alege in domeniul 10kW . 100kW. Se alege R=10k

Verificarea proiectarii prin simulare SPICE

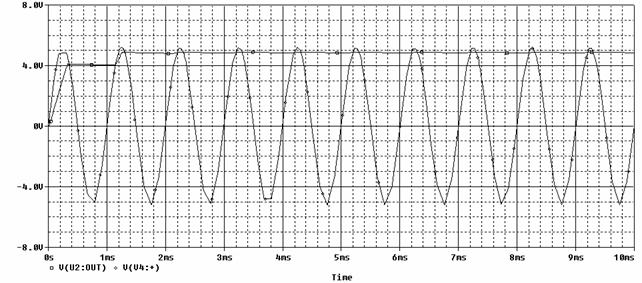

Analiza in timp a circuitului a furnizat grficul urmator. Se poate observa ca detectorul urmareste valoarea de varf a semnalului de intrare.

Verificarea valorii condensatorului de filtraj

Se numeroteaza nodurile si se descrie circuitul, respectand cerintele programului SPICE.

Se aplica la intrarea detectorului de varf (detectoarele fiind

identice se face verificarea unuia singur) un semnal sinusoidal cu amplitudinea

egala cu cea mai mare (dintre ![]() , respectiv

, respectiv ![]() ) si frecventa fJ.

Semnalul de iesire are forma din fig. 5.

) si frecventa fJ.

Semnalul de iesire are forma din fig. 5.

Se lasa RF=100kW si se modifica valoarea condensatorului CF pana cand

Se alege pentru CF o valoare standard.

Fig. 5. Forma semnalului de la iesirea detectorului de varf

S- au considerat valorile standard ale rezistoarelor si condensatorului CF= 2mF, RF= 100k si

R= 100k.

Pentru analiza circuitului

s- a considerat o sursa de tensiune sinusoidala cu o amplitudine

egala cu amplitudinea ![]() = 5.2 V si o frecventa egala cu frecventa inferioara fS=

50Hz.

= 5.2 V si o frecventa egala cu frecventa inferioara fS=

50Hz.

T se modifica valoarea condensatorului CF

pana cand

T se modifica valoarea condensatorului CF

pana cand

eroarea scade sub 1,6%.

Prin cresterea

valorii condensatorului CF pana la valoarea CF=

30,1µF eroarea care rezulta in urma simularii PSPICE va avea o

valoare sub valoarea erorii impuse in datele de proiectare, ![]()

.

.

In urma

modificarii valorii condensatorului la valoarea de CF= 30,1µF, ![]() devine

devine ![]() ,

valoare care trebuie sa fie mai mare dacat

,

valoare care trebuie sa fie mai mare dacat ![]() . Conditie indeplinita.

. Conditie indeplinita.

O alternativa la aceasta este folosirea unei rezistente RF de valoare mult mai mare, de exemplu RF= 100MΩ ceea ce inseamna inserierea a doua rezistente de 51,1MΩ.

Astfel, ![]() =2nF

=2nF

Astfel, pentru CF= 20µF si RF= 100MΩ rezulta o eroare de 1,3%.

Conditia ![]() este

indeplinita.

este

indeplinita.

Verificarea incadrarii in banda de frecventa

Cu valorile de componente corectate prin simularea SPICE anterioara se modifica frecventa semnalului la fS. Se determina valoarea tensiunii de la iesirea detectorului de varf si se compara cu valoarea ideala. Abaterea relativa trebuie sa respecte relatia

Din valorile

rezultate in urma simularii, eroarea este mai mica decat cea

impusa,  T

eroarea

T

eroarea ![]() = - 0,76%<1,6% (eroare impusa in datele de

proiectare).

= - 0,76%<1,6% (eroare impusa in datele de

proiectare).

Proiectarea multiplicatorului logaritmic

Schema de principiu

Schema de principiu a multiplicatorului logaritmic din fig. 6 contine 4 AO, dintre care 3 AO (X1, X2 si X4) intra in structura circuitelor de logaritmare iar al 4-lea AO (X3) este configurat ca circuit de exponentiere.

Circuitul este compus din doua circuite de logaritmare pentru fiecare din cele doua semnale la care se adauga un circuit pentru sursa de referinta.

Functionarea circuitelor de logaritmare si exponentiere se bazeaza pe relatia exponentiala (ecuatii Ebers-Moll), valabila pentru tranzistorul bipolar in regiunea activa directa:

unde

IS este o constanta care depinde de geometria tranzistorului;

![]() este tensiunea termica (

este tensiunea termica (![]() constanta lui Boltzmann, T temperatura

absoluta [K],

constanta lui Boltzmann, T temperatura

absoluta [K], ![]() sarcina electronului).

sarcina electronului).

Daca marimea de iesire este curentul de colector se obtine exponentierea, iar daca marimea de iesire este tensiunea baza-emitor se obtine logaritmarea, deoarece:

Fig. 6. Schema de principiu a multiplicatorului logaritmic

Tensiunea de iesire se scrie:

Tensiunea baza-emitor a tranzistorului Q3 este

![]()

unde cele doua componente sunt

respectiv

In final se poate scrie

Daca cele 4 tranzistoare fac parte dintr-o arie de tranzistoare, atunci:

tranzistoarele

lucreaza la aceeasi temperatura ![]()

tranzistoarele au

aceeasi geometrie ![]()

Se poate alege aria integrata ROB3018 (datele de catalog se afla in [2], anexa 3).

In plus, daca cele 4 rezistente sunt egale, adica ![]() , relatia tensiunii de iesire devine:

, relatia tensiunii de iesire devine:

Alegerea AO

Din motive de realizare mai usoara a montajului practic se prefera acelasi tip de AO ca cel utilizat in structura detectoarelor de varf. AO ales este TL084.

Stabilitatea circuitelor de logaritmare

=max=

max= 5.2V

=max=

max= 5.2V

I= max/R= =0,52mA

=0,52mA

gm= 40 = 40

= 40 = 20,8mS

= 20,8mS

Impedanta efectiva de reactie (fig. 7) este:

![]() W W

W W

Acest

parametru se modifica in limite largi daca si Uin

se modifica (![]() ). Astfel poate fi 26W la

). Astfel poate fi 26W la ![]() , respectiv 26MW

la

, respectiv 26MW

la ![]()

Fig. 7. Schema de principiu a circuitului de logaritmare

Este de preferat sa nu se depaseasca valoarea de 1mA a curentului prin tranzistorul Q. Rezulta pentru rezistenta R valori de ordinul kW

Se

poate alege ![]() ([2], anexa 1).

([2], anexa 1).

Datorita elementului activ din bucla de reactie circuitul de logaritmare poate oscila. Analiza stabilitatii cere determinarea factorului de reactie b care se determina pe schema echivalenta de semnal mic realizata prin pasivizarea surselor de tensiune cu exceptia sursei uT. Schema echivalenta de semnal mic se prezinta in fig. 8, a iar circuitul de calcul in fig. 8, b.

a) b)

Fig. 8. a) schema echivalenta de semnal mic; b) circuitul de determinare a factorului de reactie

Se

noteaza capacitatea echivalenta ![]()

unde: Cm/3V-> Cm/0V

CCS/3V-> CCS/0V-> CCS/15V

Aria de tranzistoare ROB3018 este o matrice de tranzistoare integrate, realizata pe un singur substrat. Aceasta matrice este adaptata pentru a oferi o flexibilitate maxima in proiectarea circuitelor pentru aplicatii de banda larga. Perfecta imperechere a tranzistoarelor si cuplajul termic permit tehnici de circuit inexistente in cazul folosirii componentelor discrete.( [2])

Principalii parametrii ai ariei ROB3018:

unde:

Ceb este capacitatea emitor- baza

Ccb este capacitatea colector- baza

CCS este capacitatea colector- substrat

Potentialele interne Yo sunt ([3], pag. 121 parametrii tipici pentru tranzistoare npn integrate, alimentate cu tensiuni pana la 20V):

la jonctiunea

emitor-baza ![]()

la jonctiunea

colector-baza ![]()

la jonctiunea

colector-substrat ![]()

Factorul de

reactie este (fig. 8,b): ![]() deoarece

deoarece ![]() .

.

Expresia

tensiunii diferentiale este  .

.

Rezulta

![]() ,

care are modulul

,

care are modulul ![]() si un zero la care

corespunde frecventa

si un zero la care

corespunde frecventa ![]() .

.

Capacitatile colector-baza si colector-substrat corespund unor jonctiuni polarizate invers si se determina cu ajutorul unei relatii de forma:

unde Co reprezinta valoarea capacitatii la tensiune de polarizare zero, C este capacitatea la tensiunea U iar Yo este diferenta interna de potential.

Tensiunea

colector-baza este egala cu zero (intrarea inversoare este punct

virtual de masa). Rezulta:

, unde

, unde

![]() = CCB=0,26pF/3V din

foile de catalog ([2], anexa 3).

= CCB=0,26pF/3V din

foile de catalog ([2], anexa 3).

Tensiunea colector-substrat este EC=15V.

Din foile de catalog se cunoaste ![]() = 2,8pF/3V. Valoarea capacitatii la

tensiunea EC este:

= 2,8pF/3V. Valoarea capacitatii la

tensiunea EC este:

Dar capacitatea echivalenta ![]() = 1,34pF+ 1,41pF= 2,75pF

= 1,34pF+ 1,41pF= 2,75pF

![]()

![]() T

T![]()

![]()

Se deseneaza caracteristicile Bode si conform regulilor prezentate in paragraful 2.3 se determina marginea de faza. Cazul cel mai defavorabil este pentru curentul de colector de valoarea cea mai mare.

Din interpretarea diagramei Bode rezulta un circuit instabil.

Marginea de faza este mf=

1800- 2250= -450. Circuitul trebuie compensat

in frecventa. Compensarea in frecventa se poate face prin

modificarea factorului ![]() . (

. (

![]() trebuie

sa devina foarte mic, aproape de 0dB W T

trebuie

sa devina foarte mic, aproape de 0dB W T ![]() =1.

=1.

Compensarea in frecventa a circuitului de logaritmare

Valoarea minima a rezistentei de reactie fiind mica, stabilizarea circuitului cu un condensator (CC) conectat in paralel cu AO (intre iesire si intrarea inversoare) necesita valori prea mari pentru capacitate. De aceea, pe langa condensatorul de compensare se monteaza si un rezistor (RC) in serie cu iesirea AO, care are rolul de a limita inferior rezistenta efectiva de reactie (fig. 9, a).

a) b)

Fig. 9. a) schema echivalenta de semnal mic; b) circuitul de determinare a factorului de reactie

Circuitul din fig. 9.b permite determinarea factorului de reactie

![]()

unde capacitatea echivalenta Ce reprezinta rezultatul legarii in paralel a capacitatilor colector-substrat si colector-baza ale tranzistorului din aria integrata de tranzistoare.

Inversul

factorului de reactie este ![]() si pune in evidenta existenta

unui zero la care corespunde frecventa

si pune in evidenta existenta

unui zero la care corespunde frecventa ![]() si a unui pol la care corespunde

frecventa

si a unui pol la care corespunde

frecventa ![]()

Pentru ![]() =0dB T

=0dB T ![]() T

T![]() T RC=R

T RC=R

fu= PAB= ft

fp= ![]()

Dimensionarea elementelor de compensare, CC si RC

Daca AO cu care se realizeaza circuitul de logaritmare are o astfel de caracteristica in bucla deschisa incat axa absciselor (a frecventelor) intersecteaza caracteristica de amplitudine in zona cu panta -20dB/dec, atunci pentru dimensionarea elementelor circuitului de compensare in frecventa se parcurg urmatoarele etape:

circuitul este stabil

daca ![]() si cunoscand valoarea

rezistentei R=10kΩ rezulta

si cunoscand valoarea

rezistentei R=10kΩ rezulta ![]() =10k

=10k

de pe caracteristica de

amplitudine a AO utilizat se evalueaza frecventa corespunzatoare

amplificarii unitare, fu. Se alege ![]() ; Se considera

; Se considera ![]()

din relatia lui fp se determina valoarea condensatorului de compensare CC.

CC= ![]() TCC=

15,9pF

TCC=

15,9pF

Se alege

valoarea standard CC= 18pF cu toleranta de ![]() .

.

conditia de

margine de faza pozitiva impune ![]() . Cu cat frecventa zeroului este mai aproape

de cea a polului, cu atat este mai sigur ca marginea de faza este

pozitiva.

. Cu cat frecventa zeroului este mai aproape

de cea a polului, cu atat este mai sigur ca marginea de faza este

pozitiva.

Se calculeaza fz :

![]()

Conditia ![]() este indeplinita .

este indeplinita .

Cu cat diferenta fP- fz este mai mica, cu atat posibilitatea ca circuitul sa fie stabil este mai mare.(

In exemplul anterior, diferenta este: fP- fz= 1MHz- 764,4kHz= 235,6kHz.

Analizam si

cazul:![]() =600kHz T

=600kHz T ![]() = 26,5pF .

= 26,5pF .

Se alege valoarea

standard CC= 26,7pF cu toleranta de ![]() . T

. T

![]()

Conditia ![]() este indeplinita .

este indeplinita .

Diferenta este: fP- fz= 600kHz- 540kHz= 60kHz. Aceasta valoare este mai mica decat in cazul anterior, in care diferenta era 235,6kHz. Rezulta ca acest caz este mai favorabil din punct de vedere al stabilitatii circuitului.

La analiza marginii de faza a circuitului de logaritmare compensat in frecventa rezulta valoarea mf= 90o. Rezulta deci un circuit stabil.

Stabilitatea circuitului de exponentiere

Schema echivalenta de semnal mic si cea de determinare a factorului de reactie se prezinta in fig. 10.

a) b)

Fig. 10. a) schema echivalenta de semnal mic a circuitului de exponentiere;

b) schema de determinare a factorului de reactie

unde rd si ro sunt parametrii de catalog ai AO ales.

Din datele de catalog, r0= 220Ω, iar Ce a fost calculat anterior, Ce= 2,75pF.

Rezistenta R are aceeasi valoare ca cea determinata la circuitele de logaritmare, R= 10k

Factorul de reactie depinde de frecventa si este

![]()

Inversul factorului de reactie pune in

evidenta modulul ![]() si un zero la care corespunde frecventa

si un zero la care corespunde frecventa

![]() =0,000005665

=0,000005665![]() 12=

12=

=5,66MHz.

Se deseneaza caracteristicile Bode. In urma analizei caracteristicii Bode a circuitului de

Exponentiere rezulta o margine de faza mf= 45o. Circuitul se afla la limita de stabilitate. Se va considera ca fiind un circuit stabil.

Compensarea offset-ului

Schema de calcul a offset-ului pentru circuitul de logaritmare se prezinta in fig. 11, a iar pentru cel de exponentiere in fig. 11, b.

a) b)

Fig. 11. Circuitele de determinare a offset-ului pentru: a) logaritmare; b) exponentiere

Din datele de catalog ale amplificatorului operational ales, TL084 avem :

UIO= 3mV6mV. Se alege UIO= 3mV

IIO= 5pA100pA. Se alege IIO= 5pA

IB= 30pA200pA. Se alege IB= 30pA

Avem relatiile :

IIO= IB+-IB-

IB=

![]() .

De aici rezulta

.

De aici rezulta ![]()

Expresia curentului de colector la logaritmare se scrie:

![]()

Tensiunea de la iesirea circuitului de exponentiere este

![]()

In ambele relatii termenul de eroare este ![]() si trebuie sa indeplineasca

conditia:

si trebuie sa indeplineasca

conditia:

![]()

![]()

Pentru circuitul de logaritmare:

UO=

0,65V. Rezulta ![]() , adica

, adica ![]() .

Relatie indeplinita.

.

Relatie indeplinita.

Pentru circuitul de exponentiere:

UO= .

Rezulta

.

Rezulta ![]() , adica

, adica ![]()

In ambele cazuri, eroarile sunt mai mici decat cele impuse in datele de proiectare. Rezulta astfel ca circuitul nu are nevoie de anulare a offset- ului.

In caz contrar se impunea anularea offset-ului (utilizand bornele proprii ale AO sau aplicand o mica tensiune continua pe intrarea fara semnal)

Verificarea prin simulare SPICE

Se face simularea SPICE pentru multiplicatorul logaritmic, aplicand la intrarile lui tensiuni continue, egale cu valorile de varf indicate in datele de proiectare.

Se verifica offset-ul la iesire (abaterea dintre valoarea obtinuta prin calcul si cea obtinuta prin simulare).

Corectia se realizeaza modificand valoarea rezistentei R4 (fig. 6).

Conditie indeplinita.

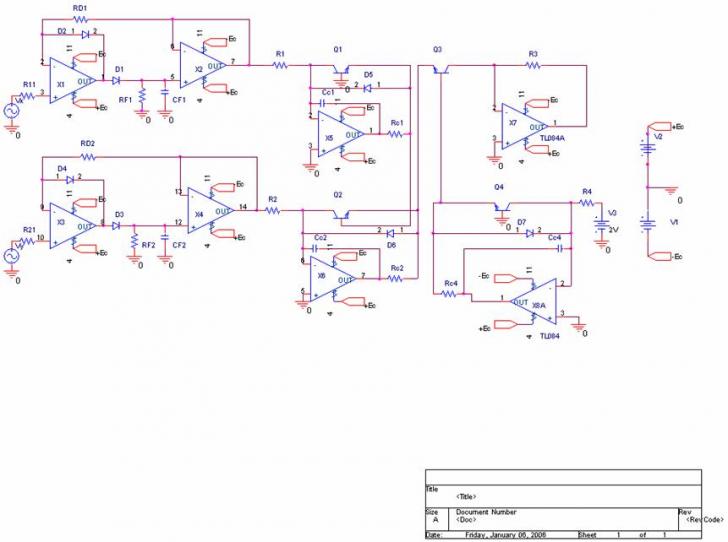

Schema reala a circuitului

Schema reala a circuitului trebuie sa contina, pe langa elementele din schemele de principiu, urmatoarele:

Modul de alimentare si condensatoarele de filtraj de pe liniile de alimentare;

Eventualele circuite de anulare a offset-ului;

Circuitele de compensare in frecventa;

O schema posibila se prezinta in fig. 12.

Alaturi de schema circuitului trebuie sa se includa si o lista de componente. Exemplu:

Lista de componente

|

Nr. crt. |

Denumire din schema |

Tip/valoare |

Caracteristici |

Buc. |

|

|

D1 D7 |

1N4148 |

dioda cu siliciu, de comutatie |

|

|

|

RF1, RF2 |

100kW |

rezistor cu pelicula de carbon, seria RCG1025, toleranta |

|

|

|

RD1, RD2 |

10kΩ |

rezistor cu pelicula de carbon, seria RCG1025, toleranta |

|

|

|

CF1, CF2 |

30,1pF |

Condensator multistrat tip I, seria MC, toleranta 5%, fara restrictii in banda de frecventa. Se utilizeaza in echipamente electronice profesionale. |

|

|

|

CC1, CC2, |

26,5pF |

Condensator multistrat tip I, seria MC, toleranta 5%, fara restrictii in banda de frecventa. Se utilizeaza in echipamente electronice profesionale. |

|

|

|

Q1 Q4 |

ROB3018 |

Aria de tranzistoare ROB3018 este o matrice de tranzistoare integrate, realizata pe un singur substrat. Aceasta matrice este adaptata pentru a oferi o flexibilitate maxima in proiectarea circuitelor pentru aplicatii de banda larga. Perfecta imperechere a tranzistoarelor si cuplajul termic permit tehnici de circuit inexistente in cazul folosirii componentelor discrete. |

|

|

|

X1 X8 |

TL084 |

Amplificator operational cu rezistenta de intrare, rd= 1012W , SR 8..13V/ms, castigul in tensiune la semnal mare |

|

Fig. 12. Schema reala a circuitului

In urma simularii in PSPICE a intregului circuit a rezultat urmatorul grafic :

Primul semnal, cu valorea de 7,1362V este rezultatul obtinut la iesirea circuitului.

Al doilea semnal,

cu valoarea de 5,1767 este valoarea tensiunii ![]()

Al treilea semnal,

cu valoarea de 2,7597 este valoarea tensiunii ![]() .

.

Rezultatul ideal este

![]()

Rezultatul real,

obtinut in urma simularii este ![]()

Propunere de cablaj imprimat

Configuratia pinilor pentru AO si aria de tranzistoare ROB3018

Se poate lucra cu circuite integrate de tipul TL081, LF155 sau ROB74 care contin un AO pe cip sau cu circuitul integrat TL084 care contine 4 AO pe cip. Configuratia pinilor pentru AO utilizate si aria de tranzistoare ROB 3018 se prezinta in fig. 13.

Fig. 13. Configuratia pinilor pentru AO utilizate si aria de tranzistoare

Semnificatia notatiilor este:

NUL = pin de anulare a offset-ului

IN- = intrare inversoare

IN+ = intrare neinversoare

OUT = iesire

V+ = pin de alimentare cu tensiune pozitiva

V- = pin de alimentare cu tensiune negativa

NC = pin neconectat

SBS (la ROB3018) = substrat

Distante intre pinii componentelor

La realizarea cablajului imprimat trebuie sa se tina seama de distantele intre pinii componentelor (fig. 14):

Fig. 14. Distante intre pinii componentelor (in mm)

Recomandari privind realizarea manuala a cablajului imprimat

La stabilirea configuratiilor traseelor conductoare si a formei pastilelor de lipire pe placa de cablaj imprimat se va tine seama de urmatoarele recomandari:

a. se vor alege traseele de cablaj cele mai scurte;

b. se vor evita unghiurile exterioare ascutite, care pot produce exfolierea suprafetei;

c. se vor evita unghiurile interioare pronuntate;

d. cand conductoarele trec printre terminale se vor mentine spatii egale intre terminale si conductoare;

e. se vor evita pastilele de lipire cu suprafata mare, deoarece pot produce probleme in procesul de lipire;

f. configuratia traseului se va mentine simetrica in jurul gaurii, in scopul producerii de lipituri simetrice;

g. raza R a pastilei de lipire va fi de 2 . 3 ori mai mare decat diametrul d al gaurii de conectare a componentei;

h. latimea l a conductorului de legatura intre pastile va fi 1/2 . 2/3 din raza R a pastilei de lipire.

Fig. 15. Stabilirea configuratiilor traseelor conductoare si a formei pastilelor de lipire

Bibliografie

1. Pana, Gh. - Indicatii date la ora de proiect;

2. Pana, Gh. Circuite Integrate Analogice. Indrumar de proiectare, Universitatea Transilvania, Brasov, 1999;

3. Gray, P. R. si Meyer, R. G. Circuite integrate analogice. Analiza si proiectare, Traducere dupa editie a III-a: Bodea, M., Editura Tehnica, Bucuresti, 1997;

4. Dragulanescu, R. Agenda radioelectronistului, Editura Tehnica, Bucuresti, 1983;

5. Radu, O. Componente electronice pasive. Catalog, Editura Tehnica, Bucuresti, 1981.

6. Szekely, G. Aparate Electronice de masurare, curs

7. Internet- https://www.actrus.ro/biblioteca/cursuri/electro/teodoru/a_9_4.html

| Contact |- ia legatura cu noi -| | |

| Adauga document |- pune-ti documente online -| | |

| Termeni & conditii de utilizare |- politica de cookies si de confidentialitate -| | |

| Copyright © |- 2025 - Toate drepturile rezervate -| |

|

|

|||||||

|

|||||||

|

|||||||

Proiecte pe aceeasi tema | |||||||

|

| |||||||

|

|||||||

|

|

|||||||